ACADL to Verilog Translation

Bachelor’s Thesis / Master’s Thesis / Student Research Project

Abstract

Abstract modeling of HW/SW systems is a relatively new research topic. This technique aims to capture only the essential parameters of software and hardware that influence their timing behavior. The Computer Architecture Description Language (ACADL) provides a method for the abstract modeling of computer hardware.

This student project’s goal is to translate the ACADL classes into (synthesizable) Verilog modules and simulate those modules using an RTL simulator and mapping them onto an FPGA.

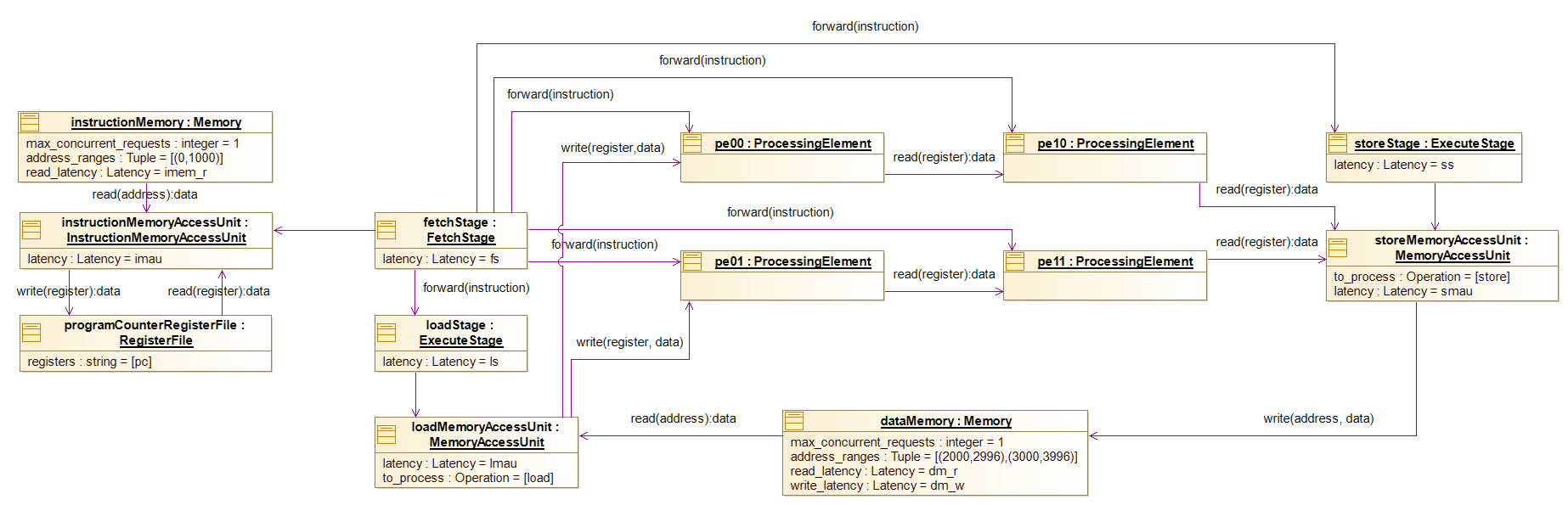

An Example of a simple machine learning accelerator modelled with ACADL is presented here:

References

Requirements

- Verilog

- Python

- Successfully atteded the lecture “Grundlagen der Rechnerarchitektur” and/or “Parallele Rechnerarchitekturen” (optional)

- Linux (optional)